공부중

NOR, NAND cmos 설계 본문

실제로 RTL 레벨로 회로를 구성하게 되면 NOR gate와 NAND gate를 사용한다.

그 이유는 무엇일까??

OR과 NOR의 게이트를 NOR과 NAND에 NOT 게이트를 연결하여 만들기 때문이다. 왜 그렇게 만드는지에 대해 알아보려면 해당 게이트를 구성하는 CMOS 구조에 대해 알고 있어야 한다.

MOSFET 소자로 반도체 칩을 설계하게 된다. 자세한 내용은 MOS 작동 원리를 검색하여 학습하고 우리는 아래와 같이 생긴 nmos와 pmos를 사용하여 회로를 설계하게 된다.

nmos는 전자를 carrier로 사용하며, pmos는 hole를 carrier로 사용한다. 이러한 carrier를 source에서 drain으로 보내게 된다.

그러면 전류는 어떻게 흐를까?

nmos는 d에서 s로, pmos는 s에서 d로 전류가 흐르게 된다.

이러한 mos로 가장 기본적인 not gate를 설계해보자.

1. not gate

같이 참고하면 좋을 것 같다. 아래 글의 사진을 보고 동작을 이해하자

https://electbros.com/cmos-logic-gate/

CMOS를 이용한 Logic Gate 구현하기 - 전자형

CMOS (Complementary MOS)는 NMOS와 PMOS로 구성된 소자입니다. 이 소자를 바탕으로 논리회로에서 사용하는 기본적인 논리게이트를 설계하는 방법에 대해서 다뤄보도록 하겠습니다.

electbros.com

0 을 입력하면 pmos와 연결되고, nmos는 오픈되어 VDD와 연결되어 1을 출력하고

1을 입력하면 pmos는 오픈되고 nmos와 연결되어 GND 즉 VSS, 즉 0을 출력한다는 것을 기억하자.

이처럼 mos를 사용하여 회로를 설계하면 입력이 반전된다는 것을 확인할 수 있다.

2. NOR gate

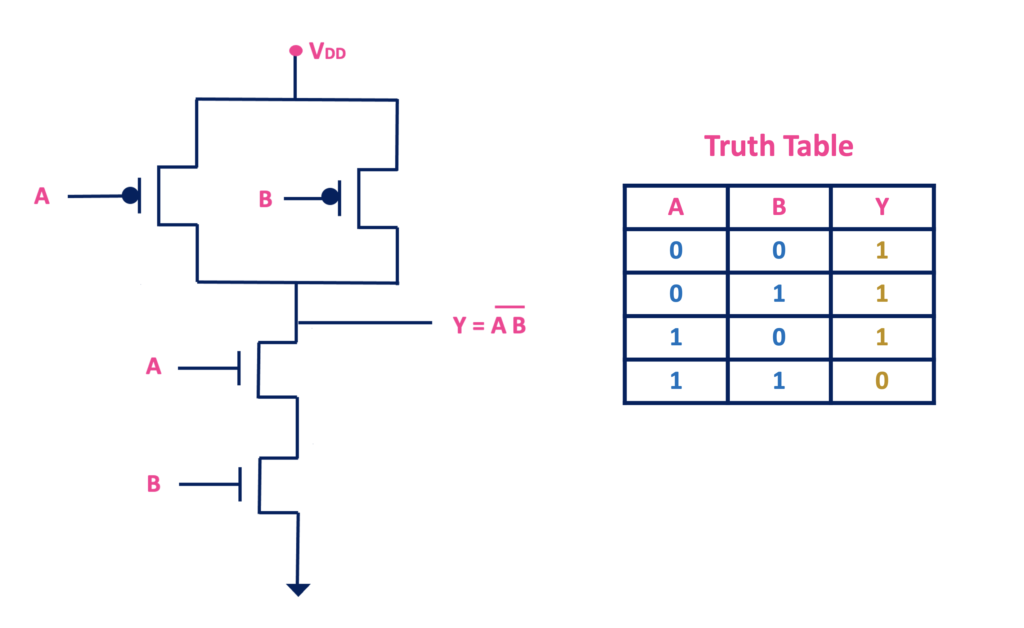

3. NAND gate

영어로 설명되어 있긴 하지만 이해를 위해서 아래의 사이트를 참고해도 좋을 것 같다.

https://www.allaboutelectronics.org/cmos-logic-gates-explained/

CMOS Logic Gates Explained

In this article, CMOS Logic is explained, and how to design different logic gates using CMOS Logic is explained in detail.

www.allaboutelectronics.org

'전자전기 > 논리 회로 보충' 카테고리의 다른 글

| RS latch cmos design (0) | 2024.04.09 |

|---|---|

| OR, AND cmos 설계 (0) | 2024.04.08 |

| flip-flop회로 (0) | 2022.11.13 |