공부중

플립플롭과 래치의 차이점 본문

Q. 플립플롭과 래치의 차이점은?

입력을 저장하는 시점(타이밍 제어 방식)이 다릅니다.

래치의 경우 Enable(혹은 클록)이 활성화된 동안만 입력을 반영하는 레벨 트리거(Level-triggered) 동작을 합니다. 이 때문에 비동기적 특성을 가집니다.

플립플롭의 경우 클록 신호의 엣지(edge), 즉 상승 엣지(rising edge) 또는 하강 엣지(falling edge)에서만 입력을 받아 상태를 바꿉니다. 입력이 바뀌더라도 클록 엣지 이전/이후에는 상태를 유지하는 엣지 트리거(Edge-triggered) 동작을 합니다. 즉 동기식 회로라고 할 수 있습니다.

| 래치(Latch) | 플립플롭(Flip-Flop) | |

| 동작 방식 | 레벨 트리거 | 엣지 트리거 |

| 제어 신호 | Enable 또는 Clock Level | Clock Edge |

| 반응 시점 | 신호가 유지되는 동안 입력 반영 | 엣지 순간에만 입력 반영 |

| 동기성 | 비동기적(asynchronous) | 동기적(synchronous) |

| 설계 시 특징 | 빠르지만 민감 → 주의 필요 | 안정적 → 복잡한 설계에 적합 |

D 래치와 D 플립플롭을 통해 위의 특성을 확인해 보겠습니다.

1. D 래치

간단한 NAND D 래치로 동작을 확인해보자

|

|

동작을 확인하기 위해 NAND는 입력이 모두 1일때만 출력이 0이며, 그 외 경우는 출력이 1임을 기억하자

진리표 동작을 하나씩 살펴보자.

CLK가 0일 때 Q와 Q'는 이전 값을 그래로 유지한다.

| CLK | D | ||

| 0 | 0 |  |

|

| 이전 Q : 0 이전 Q' : 1 |

이전 Q : 1 이전 Q' : 0 |

이때 D값을 1로 바꿔보자. 그래도 clk로 인해 중간 부분의 출력이 그래도 1을 유지하므로 최종 출력은 위와 같이 이전 출력값과 동일한 값임을 확인할 수 있다.

| CLK | D | ||

| 0 | 1 |  |

|

| 이전 Q : 0 이전 Q' : 1 |

이전 Q : 1 이전 Q' : 0 |

CLK를 1로 바꿔보자. D는 0일 때

Q = 0으로 리셋 된다.

| CLK | D | ||

| 1 | 0 |  즉 리셋된다. |

다음  다음  |

| 이전 Q : 0 이전 Q' : 1 |

이전 Q : 1 이전 Q' : 0 |

D는 1일 때,

Q는 1로 SET 된다.

| CLK | D | ||

| 1 | 1 |  다음  다음  |

|

| 이전 Q : 0 이전 Q' : 1 |

이전 Q : 1 이전 Q' : 0 |

2. D 플립플롭

|

|

그런데 왜 플립플롭은 클락의 엣지에서만 값을 저장하게 할 수 있는 것일까?

3. 플립플롭의 구조

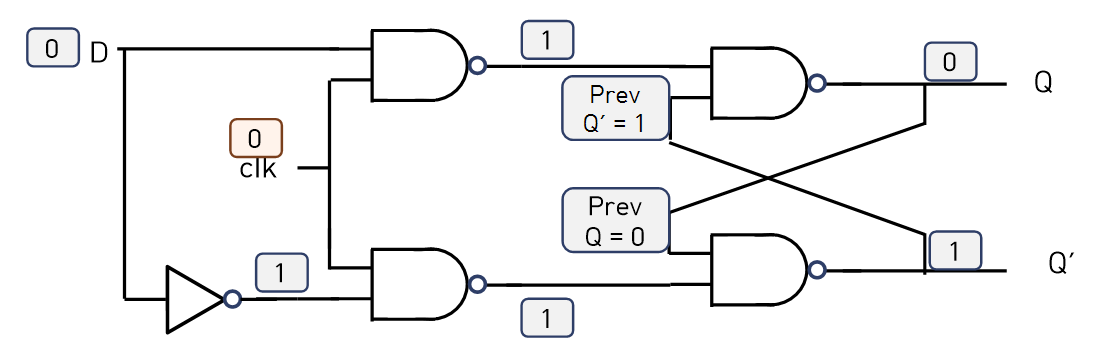

플립 플롭은 내부에 래치 2개(Master, Slave)를 직렬로 연결한 구조이다.

클락에 따라 각 래치가 어떻게 동작하는지 확인해보자.

참고로 아래 예시는 위 회로도와 다르게 클락 동작이 반대라(인버터 부분이 다릅니다) 위 회로는 상승 엣지에 동작하고, 아래 예시는 하강 엣지에 동작한다.

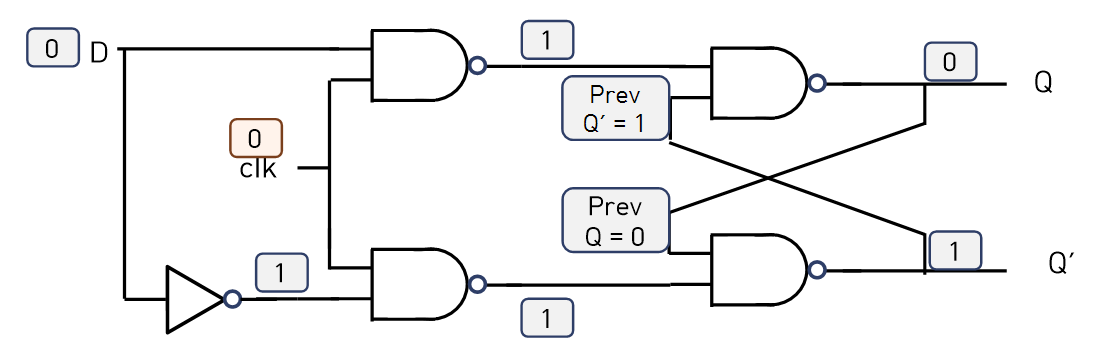

먼저 clk가 0일때를 확인해보자. 앞의 래치 동작에서 확인한 것처럼 clk가 0이면 이전 Q 값을 유지한다.

래치 동작

CLK가 0일 때 Q와 Q'는 이전 값을 그래로 유지한다.

| CLK | D | ||

| 0 | 0 |  |

|

| 이전 Q : 0 이전 Q' : 1 |

이전 Q : 1 이전 Q' : 0 |

따라서 마스터 래치는 D와 무관하게 앞의 Q 값을 계속 저장하고 있을 것이다. 반면 슬레이브 래치는 클락이 1이므로 (CLK') Q의 값에 따라 SET이나 RESET 될 것이다.

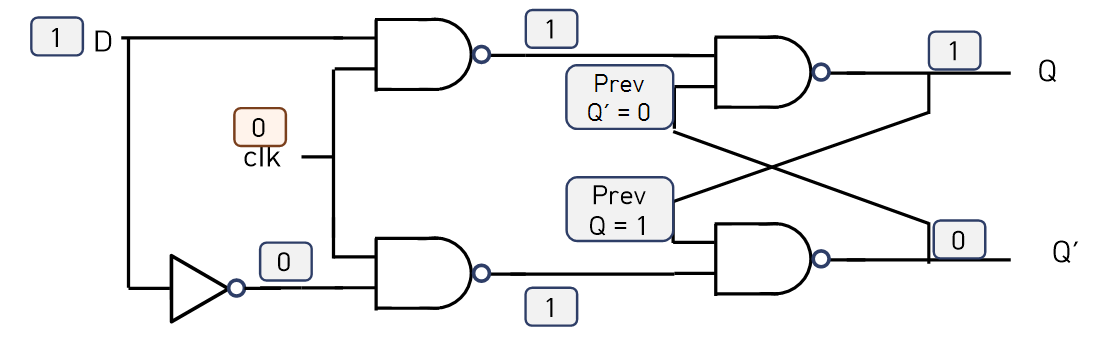

다음으로 CLK가 1일때 동작을 확인해보자.

이 때는 D 값에 따라 마스터 래치의 출력이 결정되고,

슬래이브 래치는 마스터 래치의 출력에 관계없이 이전값을 저장하게 된다.

따라서 클락에 따라 다음과 같이 동작한다.

- CLK = 0:

- Master 비활성 (고정)

- Slave 활성 (출력값 Q 유지)

- CLK 상승 중:

- Master 잠깐 활성화 (D 저장)

- Slave 비활성화로 전환 (출력 안 바뀜)

- CLK = 1 유지:

- Master 계속 활성 → D 따라가지만,

- Slave 비활성 → Q는 여전히 유지

- CLK 하강 중:

- Master 비활성화 (D 고정)

- Slave 다시 활성화 → Master의 최종 값 Q에 반영

즉, 엣지 순간(Master → Slave로 전이되는 순간)에만 데이터가 흘러갑니다.

이 구조 덕분에 불안정 상태나 글리치 없이 안정적인 동기 회로를 만들 수 있다.

더 많은 회로는 아래 글 참고

https://ko.wikipedia.org/wiki/%ED%94%8C%EB%A6%BD%ED%94%8C%EB%A1%AD

플립플롭 - 위키백과, 우리 모두의 백과사전

위키백과, 우리 모두의 백과사전. R1, R2 = 1 kΩ, R3, R4 = 10 kΩ SR 래치, NOR 논리 게이트 서로 교차 되먹임 입력으로 구성된다. 플립플롭 또는 래치(영어: flip-flop 또는 latch)는 전자공학에서 1 비트의 정

ko.wikipedia.org

https://www.build-electronic-circuits.com/d-flip-flop/

The D Flip-Flop (Quickstart Tutorial)

This is a D flip-flop tutorial for beginners. Learn how to build practical circuits like a ring counter with this simple guide.

www.build-electronic-circuits.com

'전자전기 > 논리 회로 보충' 카테고리의 다른 글

| PULSE - 펄스폭, 상승 시간 , 하강 시간 (0) | 2025.05.13 |

|---|---|

| Setup time과 Hold time 차이 (0) | 2025.05.09 |

| RS latch cmos design (0) | 2024.04.09 |

| OR, AND cmos 설계 (0) | 2024.04.08 |

| NOR, NAND cmos 설계 (0) | 2024.04.07 |