공부중

[SAR ADC] 논문 : Monotonic Capacitor Switching Procedure - 2. ADC Architecture 본문

[SAR ADC] 논문 : Monotonic Capacitor Switching Procedure - 2. ADC Architecture

복습 2024. 12. 2. 00:46A 10-bit 50-MS/s SAR ADC With a Monotonic Capacitor Switching Procedure

모노톤 커패시터 스위칭 절차를 적용한 10비트 50MS/s SAR ADC

이전 글 : https://brush-up.tistory.com/242

ADC Architecture

To achieve 10-bit accuracy, a fully differential architecture suppresses the substrate and supply noise and has good common-mode noise rejection. SAR ADCs usually use a binary-weighted capacitor array rather than a C-2C capacitor array for better linearity. Fig. 1 shows a conventional 10-bit fully differential SAR ADC. The fundamental building blocks are the comparator, sample-and-hold (S/H) circuit, capacitor network, and successive approximation registers. In this charge-redistribution based architecture, the capacitor network serves as both a S/H circuit and a reference DAC capacitor array. Therefore, this architecture does not require a monolithic S/H circuit. Since this ADC is fully differential, the operation of the two sides is complementary. For simplicity, only the positive side of the ADC operation is described below. At the sampling phase, the bottom plates of the capacitors are charged to Vip, and the top plates are reset to the common-mode voltage Vcm. Next, the largest capacitor C1 is switched to Vref and the other capacitors are switched to ground. The comparator then performs the first comparison. If Vip is higher than Vin, the most significant bit (MSB) B1 is 1. Otherwise, B1 is 0, and the largest capacitor is reconnected to ground. Then, the second largest capacitor C2 is switched to Vref. The comparator does the comparison again. The ADC repeats this procedure until the least significant bit (LSB) is decided. Although the trial-and-error search procedure is simple and intuitive, it is not an energy efficient switching scheme, especially when unsuccessful trials occur.

10비트 정확도를 달성하기 위해, 완전 차동 아키텍처는 기판 및 공급 잡음을 억제하고 좋은 공통 모드 잡음 제거 능력을 가집니다. SAR ADC는 일반적으로 더 나은 선형성을 위해 C-2C 커패시터 배열 대신 이진 가중 커패시터 배열을 사용합니다. 그림 1은 전통적인 10비트 완전 차동 SAR ADC를 보여줍니다. 기본 구성 요소는 비교기, 샘플-앤-홀드(S/H) 회로, 커패시터 네트워크, 그리고 연속 근사 레지스터입니다. 이 충전 재분배 기반 아키텍처에서 커패시터 네트워크는 S/H 회로와 참조 DAC 커패시터 배열 모두로 기능합니다. 따라서 이 아키텍처는 일체형 S/H 회로가 필요하지 않습니다. 이 ADC는 완전 차동이므로 두 측면의 작동은 상호 보완적입니다. 단순함을 위해 ADC 작동의 양성 측만 아래에 설명됩니다. 샘플링 단계에서, 커패시터의 하단 판은 Vip로 충전되고, 상단 판은 공통 모드 전압 Vcm으로 리셋됩니다. 다음으로, 가장 큰 커패시터 C1은 Vref로 전환되고 다른 커패시터들은 접지로 전환됩니다. 그 후 비교기는 첫 비교를 수행합니다. Vip가 Vin보다 높으면 가장 중요한 비트(MSB) B1은 1입니다. 그렇지 않으면 B1은 0이며, 가장 큰 커패시터는 다시 접지로 연결됩니다. 그 다음, 두 번째로 큰 커패시터 C2가 Vref로 전환됩니다. 비교기는 다시 비교를 수행합니다. ADC는 최소 중요 비트(LSB)가 결정될 때까지 이 절차를 반복합니다. 비록 시행착오 검색 절차가 단순하고 직관적이지만, 특히 실패한 시도가 발생할 때 에너지 효율적인 전환 방식은 아닙니다.

Fig. 2 shows the proposed SAR ADC, where the proposed switching procedure can be either upward or downward. For fast reference settling, i.e., discharging through n-type transistors, downward switching was selected in this ADC. The proposed ADC samples the input signal on the top plates via bootstrapped switches, which increases the settling speed and input bandwidth. At the same time, the bottom plates of the capacitors are reset to Vref. Next, after the ADC turns off the bootstrapped switches, the comparator directly performs the first comparison without switching any capacitor. According to the comparator output, the largest capacitor C1 on the higher voltage potential side is switched to ground and the other one (on the lower side) remains unchanged. The ADC repeats the procedure until the LSB is decided. For each bit cycle, there is only one capacitor switch, which reduces both charge transfer in the capacitive DAC network and the transitions of the control circuit and switch buffer, resulting in smaller power dissipation. The flow chart of the proposed successive-approximation procedure is shown in Fig. 3.

그림 2는 제안된 SAR ADC를 보여주며, 여기서 제안된 전환 절차는 상향 또는 하향일 수 있습니다. 빠른 참조 안정화를 위해, 즉 n형 트랜지스터를 통한 방전을 위해, 이 ADC에서는 하향 전환을 선택했습니다. 제안된 ADC는 부트스트랩 스위치를 통해 입력 신호를 상단 판에서 샘플링하여, 안정화 속도와 입력 대역폭을 증가시킵니다. 동시에 커패시터의 하단 판은 Vref로 리셋됩니다. 다음으로, ADC가 부트스트랩 스위치를 끄면, 비교기는 어떤 커패시터도 전환하지 않고 바로 첫 비교를 수행합니다. 비교기 출력에 따라, 더 높은 전압 잠재력 쪽에 있는 가장 큰 커패시터 C1은 접지로 전환되고, 다른 하나(더 낮은 쪽)는 변경되지 않습니다. ADC는 LSB가 결정될 때까지 절차를 반복합니다. 각 비트 사이클에는 단 하나의 커패시터 스위치만 있어, 커패시티브 DAC 네트워크에서의 전하 전달 및 제어 회로와 스위치 버퍼의 전환을 줄이므로 전력 소모가 줄어듭니다. 제안된 연속 근사 절차의 흐름도는 그림 3에 나와 있습니다.

One of the major differences between the proposed method and the conventional one is that the common-mode voltage of the reference DAC gradually decreases from half Vref to ground as shown in Fig. 4. The proposed switching sequence does not require upward transition. At the same transistor size, the on-resistance of a nMOS switch is only about 1/3 that of a pMOS one. Having no upward transition speeds up the DAC settling. In addition, since sampling is done on the top plate, the comparator can do the first comparison without any capacitor switching. For an n-bit ADC, the number of unit capacitors in a capacitor array is 2n−1, only half that of the conventional one.

제안된 방법과 전통적인 방법 사이의 주요 차이점 중 하나는 참조 DAC의 공통 모드 전압이 그림 4에서 보여주듯이 Vref의 절반에서 접지로 점차 감소한다는 것입니다. 제안된 전환 순서는 상향 전환을 필요로 하지 않습니다. 동일한 트랜지스터 크기에서, nMOS 스위치의 온 저항은 pMOS 스위치의 약 1/3에 불과합니다. 상향 전환을 하지 않음으로써 DAC 안정화 속도가 빨라집니다. 또한, 샘플링이 상단 판에서 이루어지기 때문에, 비교기는 어떠한 커패시터 전환도 없이 첫 비교를 수행할 수 있습니다. n비트 ADC의 경우, 커패시터 배열의 단위 커패시터 수는 2^n−1로, 전통적인 방법의 절반에 불과합니다.

Fig. 5 shows 3-bit examples of the conventional and proposed switching methods. The conventional switching method is based on a trial-and-error search procedure. Fig. 5(a) shows all possible conversions. The quantitative energy consumption of each switching phase is also shown in the figure. The conventional switching sequence is efficient when all the attempts are successful, as in the upper cases. However, the switching sequence consumes a lot of energy when attempts are unsuccessful, as in the lower cases. Fig. 5(b) shows all possible switching cases of the proposed method. After the sampling switches turn off, the comparator directly performs the first comparison without switching any capacitor. Therefore, the proposed switching sequence consumes no energy before the first comparison. In contrast, the conventional sequence consumes 4CV2ref before the first comparison. The subsequent switching sequence of the proposed method is also more efficient than that of the conventional one.

그림 5는 전통적인 방법과 제안된 방법의 3비트 예시를 보여줍니다. 전통적인 전환 방법은 시행착오 검색 절차에 기반합니다. 그림 5(a)는 모든 가능한 변환을 보여주며, 각 전환 단계의 정량적 에너지 소비도 그림에 나타나 있습니다. 전통적인 전환 순서는 상단 예시와 같이 모든 시도가 성공할 때 효율적입니다. 그러나 하단 예시와 같이 시도가 실패할 때 많은 에너지를 소비합니다. 그림 5(b)는 제안된 방법의 모든 가능한 전환 사례를 보여줍니다. 샘플링 스위치가 꺼진 후, 비교기는 어떤 커패시터도 전환하지 않고 바로 첫 비교를 수행합니다. 따라서 제안된 전환 순서는 첫 비교 전에 에너지를 전혀 소비하지 않습니다. 반면, 전통적인 순서는 첫 비교 전에 4CV^2_ref의 에너지를 소비합니다. 제안된 방법의 후속 전환 순서도 전통적인 것보다 더 효율적입니다.

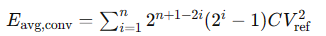

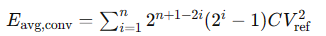

For an n-bit conventional SAR ADC, if each digital output code is equiprobable, the average switching energy can be derived as

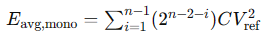

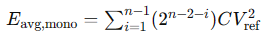

The average switching energy for an n-bit SAR ADC using the proposed switching procedure can be derived as

n 비트의 기존 SAR ADC의 경우, 각 디지털 출력 코드가 동등한 경우, 평균 스위칭 에너지는 다음과 같이 도출될 수 있습니다

제안된 스위칭 절차를 이용한 n-비트 SAR ADC의 평균 스위칭 에너지는 다음과 같이 도출할 수 있습니다

전통적인 SAR ADC의 스위칭 에너지 계산 (식 1)전통적인 n비트 SAR ADC의 평균 스위칭 에너지 공식은 다음과 같습니다:이 공식은 각 커패시터가 변환 과정에서 중요도에 따라 스위칭될 때 소비되는 에너지를 반영합니다. 항은 중요도가 감소함에 따라 커패시터의 에너지 기여도가 줄어드는 것을 조정합니다 (즉, MSB에서 LSB로). 제안된 SAR ADC 스위칭 에너지 계산 (식 2)보다 효율적인 스위칭 전략을 사용하는 제안된 SAR ADC의 평균 에너지 공식은 다음과 같습니다:이 방정식은 총 커패시터 스위칭 수를 줄여 에너지 소비를 낮추는 더 효율적인 스위칭 전략을 기반으로 합니다. 이 시퀀스의 각 단계는 현재 결정되고 있는 비트를 해결하는 데 필요한 커패시터만을 스위칭합니다. 에너지 비교이 두 방정식의 주요 차이점은 ADC 변환 과정 동안 소비되는 총 에너지에 큰 영향을 미치는 지수 요인에 있습니다. 전통적인 방법은 과정 전반에 걸쳐 더 많은 커패시터를 스위칭하여 에너지 소비가 높습니다. 반면에, 제안된 방법은 사이클 당 스위치 수를 줄여 상당한 에너지 절약을 제공합니다.이 에너지 계산은 특히 배터리를 사용하거나 에너지에 민감한 응용 프로그램에서 전력 효율이 중요한 저전력 전자 제품을 설계할 때 중요합니다. 제안된 스위칭 방법은 소비 전력을 줄임으로써 휴대용 전자 장치 및 빈번한 ADC 사용이 필요한 시스템의 성능과 실행 가능성을 크게 향상시킬 수 있습니다. |

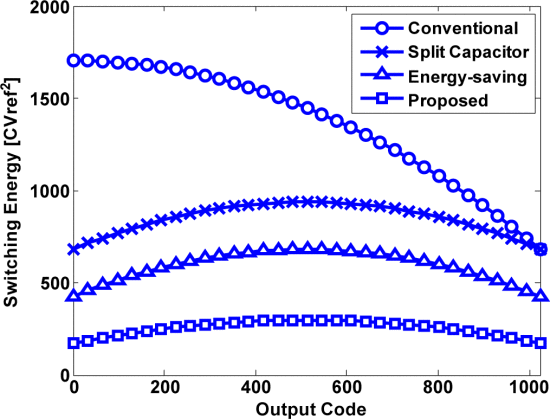

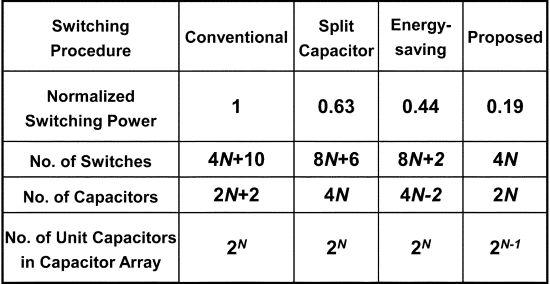

For a 10-bit case, the conventional switching procedure consumes 1365.3 CV2ref while the proposed switching procedure consumes only 255.5 CV2ref. The proposed technique thus requires 81% less switching energy than that of the conventional one. Split capacitor [4] and energy-saving [13] switching methods provide only 37% and 56% reductions, respectively. Fig. 6 shows a comparison of switching energy for the four methods versus the output code. The proposed method has the best power efficiency. Table I summarizes the features of the four methods. The proposed architecture not only has the lowest switching power consumption but also the fewest switches and unit capacitors, which simplifies digital control logic. Therefore, the proposed ADC is very hardware efficient as well.

10비트 사례에서, 전통적인 전환 절차는 1365.3 CV^2_ref의 에너지를 소비하는 반면, 제안된 전환 절차는 단지 255.5 CV^2_ref를 소비합니다. 따라서 제안된 기술은 전통적인 방법보다 스위칭 에너지를 81% 적게 필요로 합니다. 분할 커패시터 [4] 및 에너지 절약 [13] 전환 방법은 각각 37%와 56%의 감소만 제공합니다. 그림 6은 네 가지 방법에 대한 출력 코드 대비 스위칭 에너지 비교를 보여줍니다. 제안된 방법은 가장 좋은 전력 효율을 가집니다. 표 I은 네 가지 방법의 특징을 요약합니다. 제안된 아키텍처는 스위칭 전력 소비가 가장 낮을 뿐만 아니라 스위치와 단위 커패시터 수도 가장 적어 디지털 제어 논리를 단순화합니다. 따라서 제안된 ADC는 하드웨어 효율성도 매우 뛰어납니다.

논문 링크 : https://ieeexplore.ieee.org/document/5437496

A 10-bit 50-MS/s SAR ADC With a Monotonic Capacitor Switching Procedure

ieeexplore.ieee.org